ECE @ Carnegie Mellon · 2028

Joshua Taylor

Hardware & Software

Building systems at the boundary of silicon and software — verification, embedded, and the things in between.

experience

Software Development Intern

Ford Motor Company

Summer 2026

IT Architecture & Systems Engineering Intern

BWX Technologies

Summer 2025

Evaluated Microsoft CoPilot Studio and Power Automate for production readiness in a Government Cloud environment. Built an AI-powered resume screening tool for HR and an AI ticket response tool for the help desk. Applied government data security standards throughout.

selected builds

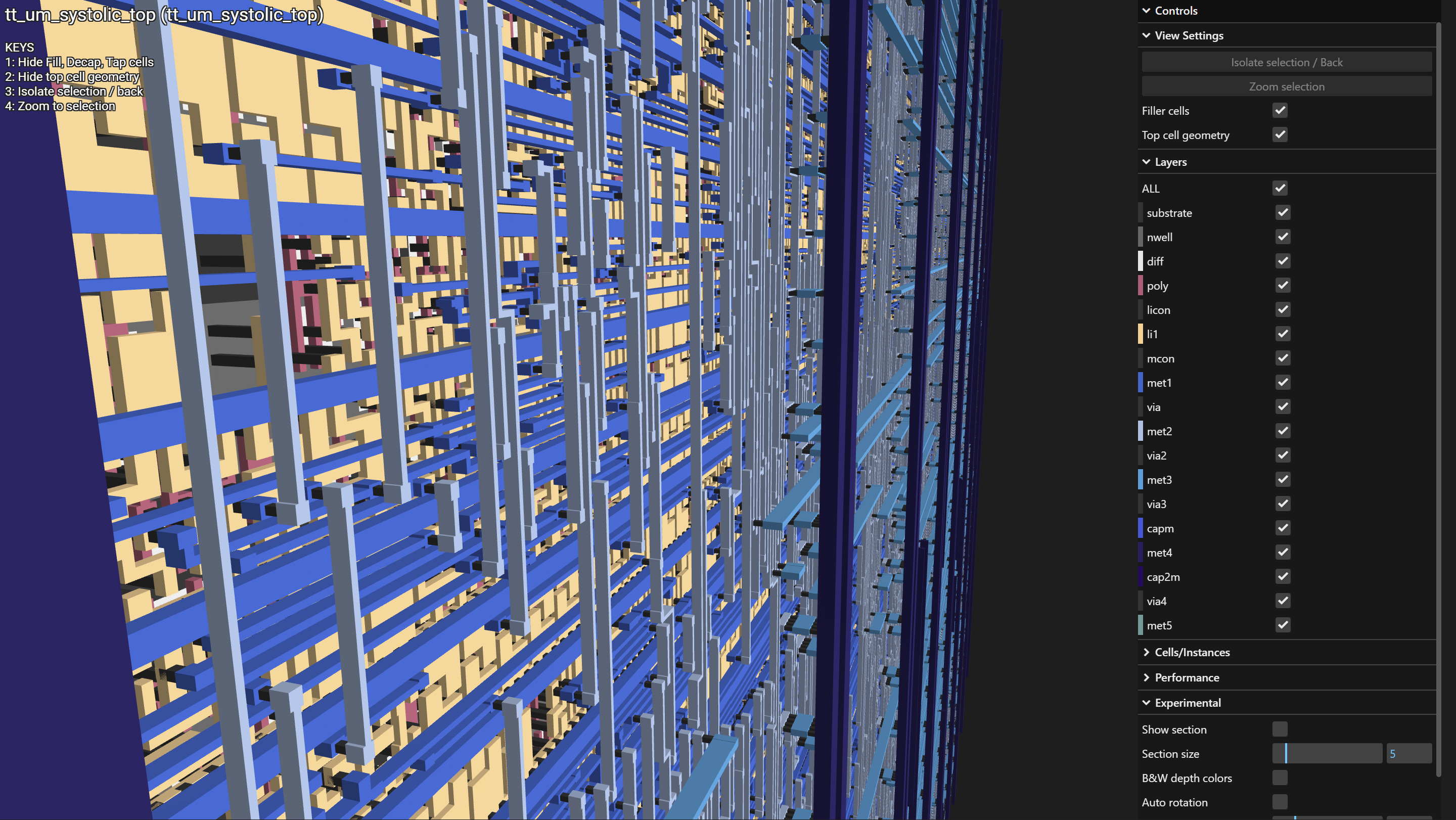

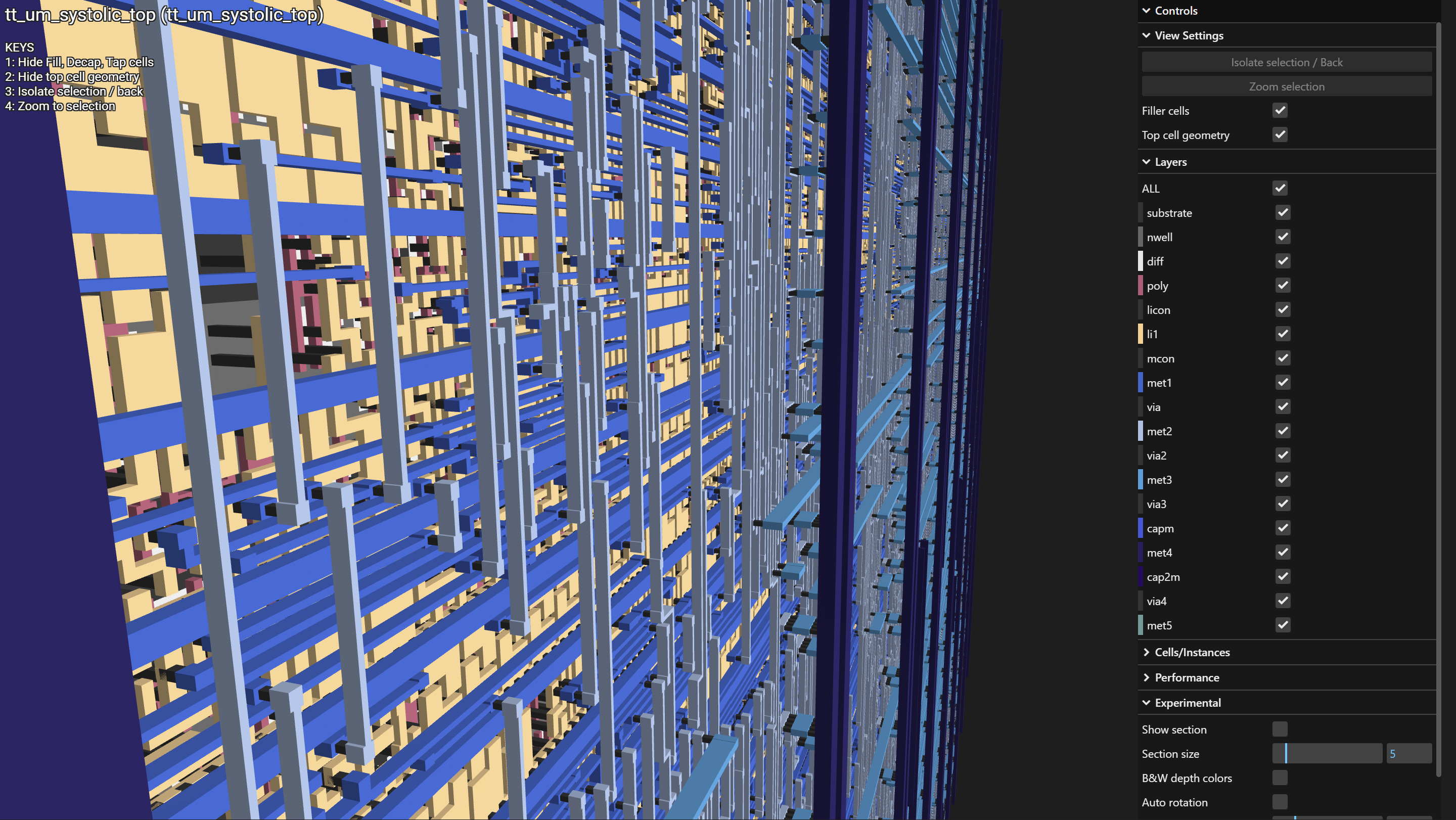

4×4 Systolic Matrix MAC

Fully pipelined 4×4 systolic array MAC accelerator in SystemVerilog submitted to the Tiny Tapeout TTSKY26a community silicon shuttle — 16 processing elements in a weight-stationary dataflow with SPI control and a custom FSM. Submitted and awaiting silicon.

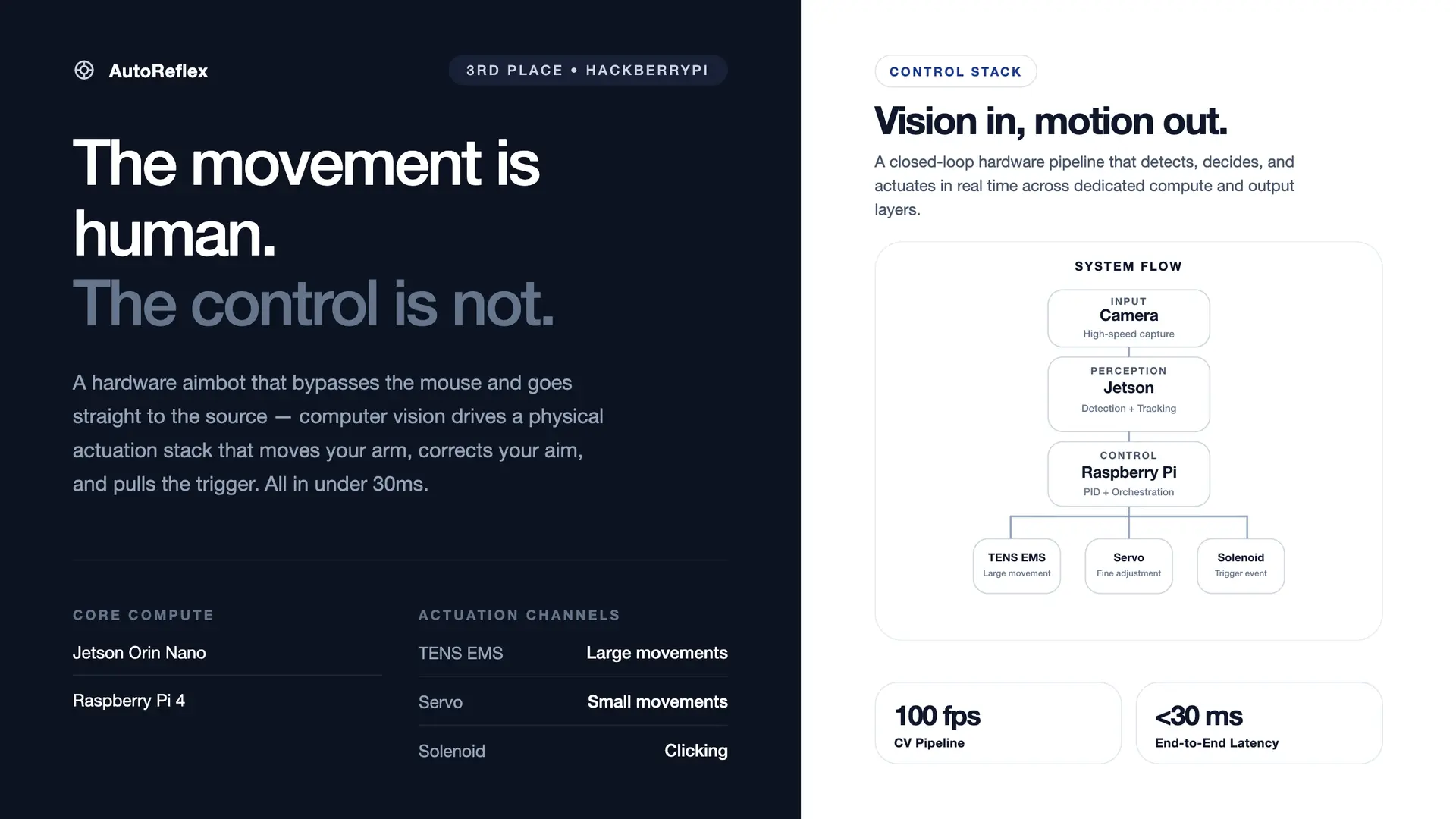

AI-Powered Aim Assist System

Jetson Orin Nano + global shutter camera + EMS actuators. Dual-mode PID controller running at 1kHz and SPI digital potentiometers for precise muscle stimulation control, achieving a 15ms pixel-to-stimulation response time.

FPGA Neural Network Accelerator

INT8 MLP running live on a Basys3 Artix-7 FPGA. Draw a digit in the browser — 784 bytes stream over UART at 115200 baud, the hardware runs inference through a 784→128→64→10 network, and returns the prediction with raw logit scores in ~78ms.

8-bit RISC-V Processor

Full processor implementation in Verilog on Basys3 FPGA. Includes instruction decoder, testbench, and SystemVerilog FSM design.

PCB Design & Fabrication

Designed and fabricated a PCB with defined test patterns, going end-to-end from schematic to physical board via JLCPCB with full BOM and CPL files.

stack

LANGUAGES

SystemVerilog

Python

C / C++

MATLAB

HARDWARE

Basys3 FPGA

Jetson Orin

Raspberry Pi

Eagle / JLCPCB

SKY130 Tapeout

CONCEPTS

RTL Design

PID Control

SPI / UART

TOOLS

Git / GitHub

Linux

Vivado

VS Code

Let’s connect.

jtaylor3@andrew.cmu.edu